# Projet de Fin d'études

Traitement du signal et communication numérique sur FPGA

### Traitement du signal et communication numérique sur FPGA

# Présentation du stage

- Contexte

- Finalité

Analyse spectrale voie courte/voie longue sur PPGA

Liaison Gigabit Ethernet sur FPGA

Conclusion et perpectives

PGA: Composant logique programmable

### Traitement du signal et communication numérique sur FPGA

# Présentation du stage

#### Thales

Un des leaders mondial en électronique pour:

- l'aéronautique

- l'espace

- la défense

- les technologies de l'information

68 000 personnes dont 22 000 ingénieurs à travers le monde

### Traitement du signal et communication numérique sur FPGA

Présentation du stage

# Division aéronautique

~ 25 % du chiffre d'affaire

Propose une gamme d'équipements et de sous systèmes dont:

- Radars de guerre électronique et de surveillance maritime

- Planches de bord

- Cockpits

### Traitement du signal et communication numérique sur FPGA

# Présentation du stage

# Service architecture numérique

Plus de 30 personnes

Conception et intégration de coffrets électronique autours de en 3 pôles:

- Pôle ingénierie

- Pôle CLP (Composant Logique Programmable)

- Pôle Programme

# Traitement du signal et communication numérique sur FPGA

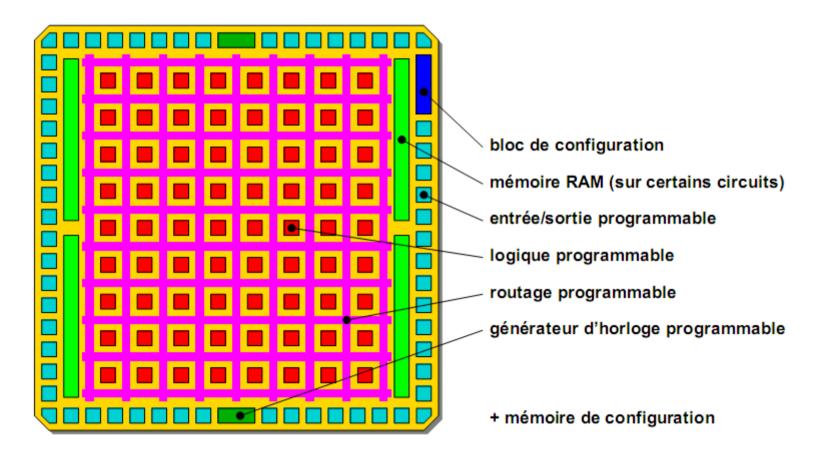

Présentation du stage Structure d'un FPGA:

# Traitement du signal et communication numérique sur FPGA

Présentation du stage

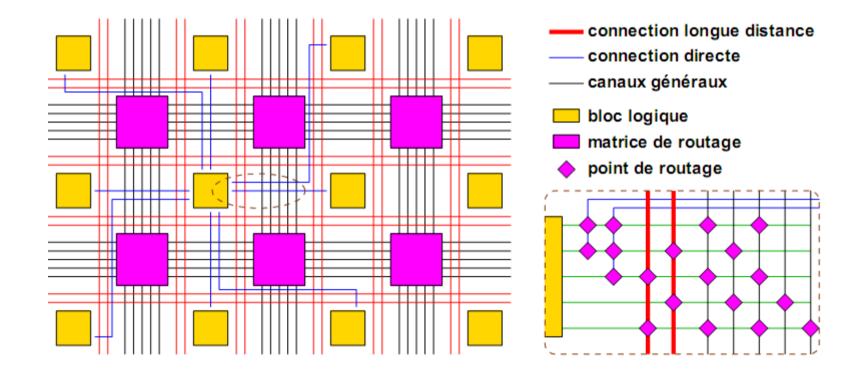

Matrice d'un FPGA:

# Traitement du signal et communication numérique sur FPGA

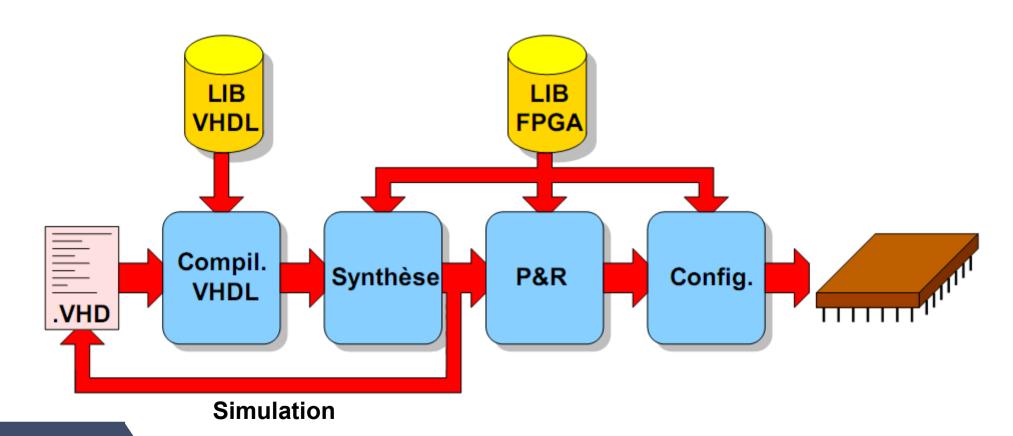

Présentation du stage Flot de conception d'un FPGA:

### Traitement du signal et communication numérique sur FPGA

# Présentation du stage

- Contexte

- Finalité

Analyse spectrale voie courte/voie longue sur PPGA

Liaison Gigabit Ethernet sur FPGA

Conclusion et perpectives

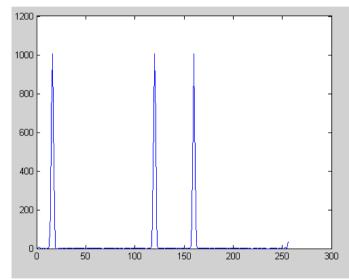

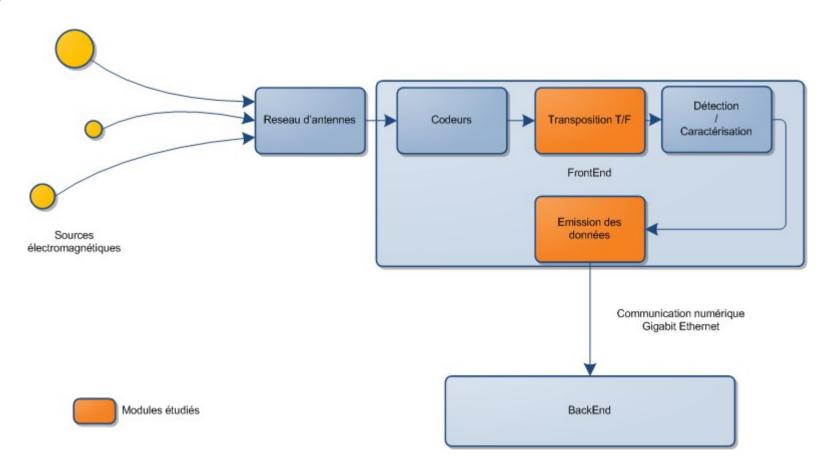

# Traitement du signal et communication numérique sur FPGA

Présentation du stage

- Finalité

Récepteur de Guerre electronique:

Codeurs

Transposition T/F

- -Analyse spectrale

- -Liaison Gigabit Ethernet

Détection

BackEnd

# Traitement du signal et communication numérique sur FPGA

### Présentation du stage

- Finalité

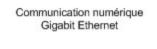

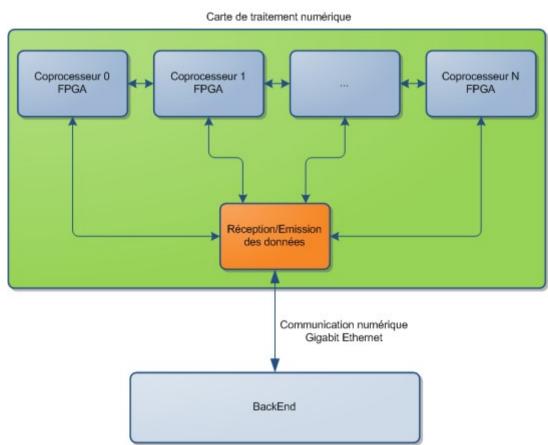

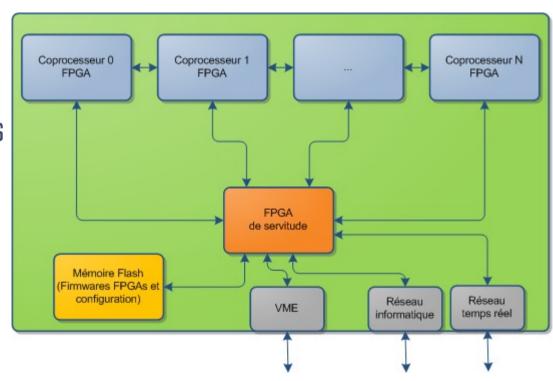

#### Carte de traitement

-Améloration de l'existant par l'adjonction d'une connectivité G-Ethernet

### Traitement du signal et communication numérique sur FPGA

Présentation du stage

- Contexte

- Finalité

Analyse spectrale voie courte/voie longue sur FPGA

Liaison Gigabit Ethernet sur FPGA

Conclusion et perpectives

# Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA

**But**: Transposer le signal temporel dans le domaine fréquentiel pour une connaissance du milieu radioélectrique.

**Résolution Fréquentielle** : Augmente avec le nombre de points intervenants dans le calcul de la FFT.

**Résolution Temporelle** : Inversement proportionnelle à la résolution Fréquentielle.

Un savant compromis est nécessaire, sauf si ...

FFT: Tranformée de Fourier Rapide

# Traitement du signal et communication numérique sur FPGA

#### Analyse spectrale voie courte/voie longue sur PPGA

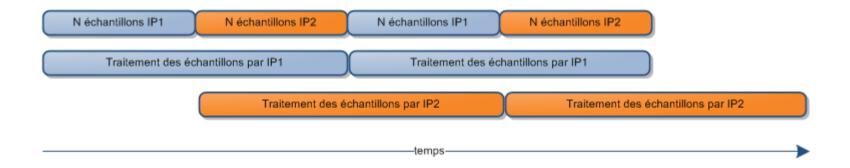

Résolution temporelle et Fréquencielle élevée--> 2 voies d'analyse:

Voie d'analyse longue

bonne résolution Fréquentielle

--> distinction de menaces de Fréquences proches

Voie d'analyse courte

bonne résolution temporelle

--> détermination précise du temps d'arrivée de la menace

# Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA

- Démarche de conception adoptée:

- Identification des contraintes et architecture du design en conséquence

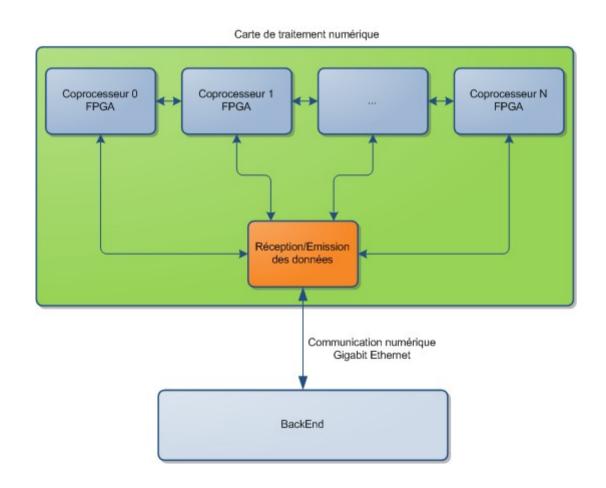

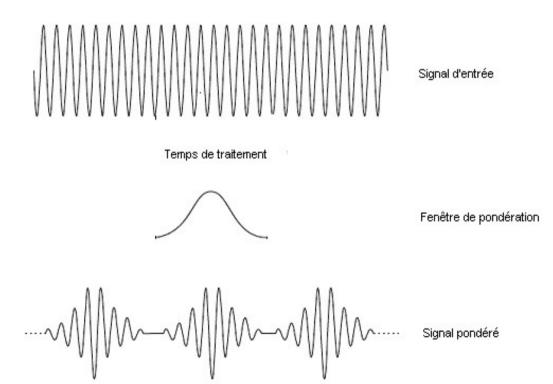

- I) Mise en forme des données

- -Fenêtrage et overlapping

- 2) Cible Visée : Virtex 5 SX95T

- -Limitation en ressources et en Fréquence de Fonctionnement

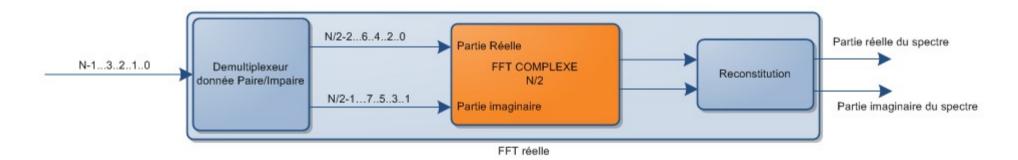

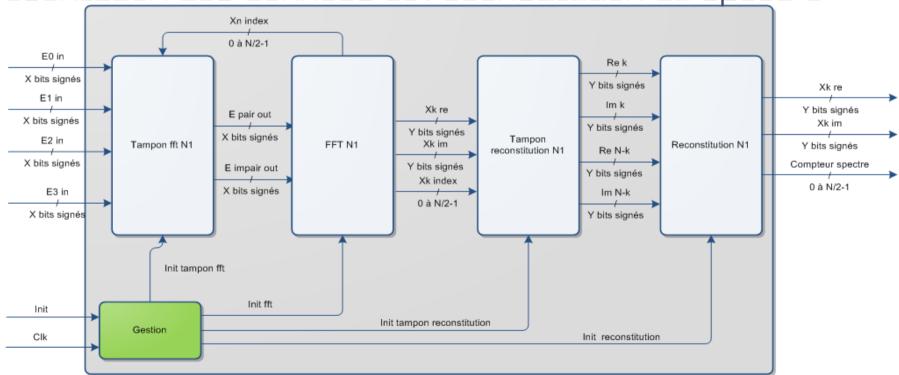

- 3) Utilisation d'une FFT complexe

- -Présentation des données et reconstitution du spectre

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA

- I) Mise en Forme des données

- -Fenêtrage et overlapping

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur FPGA

- I) Mise en Forme des données

- -Fenêtrage et overlapping

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur FPGA

2) Cible Visée : Virtex 5 SX95T

- -Temps réel

- -Limitation en ressources et en Fréquence de Fonctionnement

### Fréquence de Fonctionnement :

- supérieure à 200 Mhz

- impose 4 voies de traitement en // pour tenir la Fréquence d'échantillonnage.

#### Ressources:

- Facteur limitant: 640 DSPs

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur FPGA

### 3) Utilisation d'une FFT complexe

-Présentation des données et reconstitution du spectre

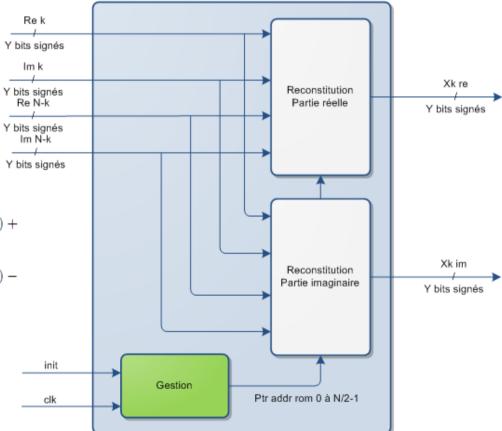

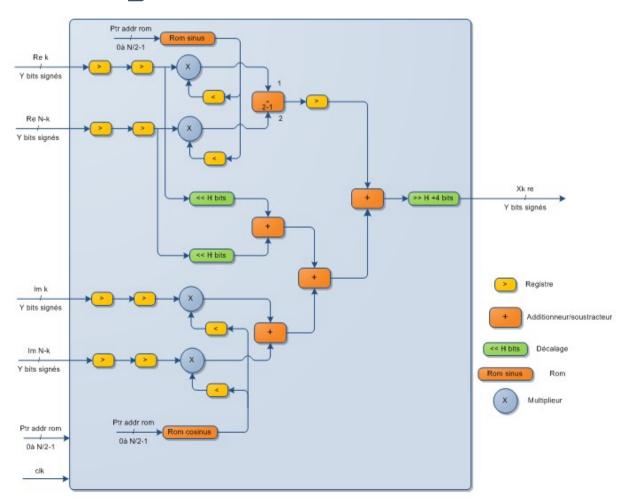

#### Algorithme de reconstitution

$$\begin{array}{l} Re(S(k)) = \frac{1}{2}.(Re(k) + Re(N-k) + Im(k).cos(\frac{\pi.k}{N}) + Im(N-k).cos(\frac{\pi.k}{N}) - Re(k).sin(\frac{\pi.k}{N}) + Re(N-k).sin(\frac{\pi.k}{N})) \end{array}$$

$$Im(S(k)) = \frac{1}{2}.(Im(k) - Im(N-k) + Re(k).cos(\frac{\pi.k}{N}) + Re(N-k).cos(\frac{\pi.k}{N}) - Im(k).sin(\frac{\pi.k}{N}) - Im(N-k).sin(\frac{\pi.k}{N}))$$

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA

### 3) Utilisation d'une FFT complexe

-Présentation des données et reconstitution du spectre

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur FPGA

### 3) Utilisation d'une FFT complexe

-Présentation des données et reconstitution du spectre

--> 4 FTs courtes pour la voie courte 4 FTs longues pour la voie longue

# Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA

-Reconstitution

### Formule:

$Re(S(k)) = \frac{1}{2}.(Re(k) + Re(N-k) + Im(k).cos(\frac{\pi.k}{N}) + Im(N-k).cos(\frac{\pi.k}{N}) - Re(k).sin(\frac{\pi.k}{N}) + Re(N-k).sin(\frac{\pi.k}{N}))$

$$Im(S(k)) = \frac{1}{2}.(Im(k) - Im(N-k) + Re(k).cos(\frac{\pi.k}{N}) + Re(N-k).cos(\frac{\pi.k}{N}) - Im(k).sin(\frac{\pi.k}{N}) - Im(N-k).sin(\frac{\pi.k}{N}))$$

# Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA

-Reconstitution partie réelle

Pipelinage du calcul

Latence de 8 coups d'horloge

# Traitement du signal et communication numérique sur FPGA

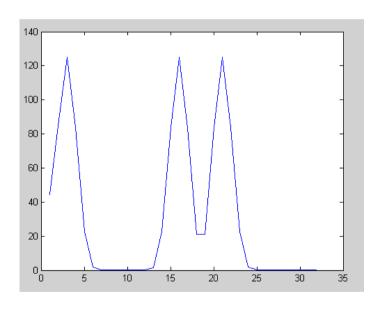

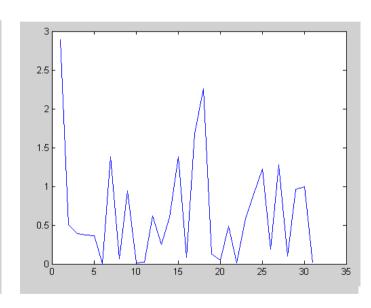

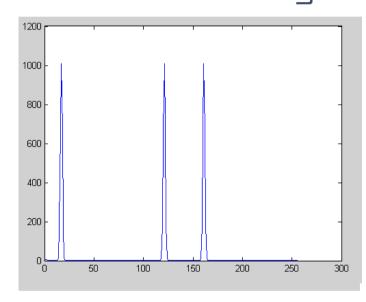

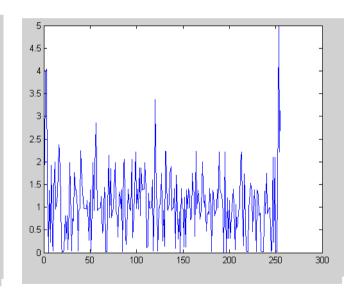

Analyse spectrale voie courte/voie longue sur FPGA -Résultats voie courte

matlab

simulation modelsim

erreur absolue

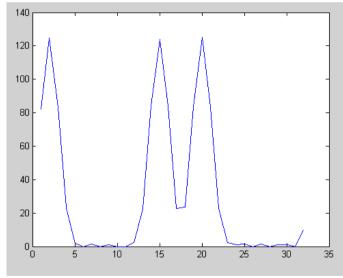

# Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur FPGA -Résultats voie longue

matlab

simulation modelsim

erreur absolue

### Traitement du signal et communication numérique sur FPGA

Analyse spectrale voie courte/voie longue sur PPGA -Résultats

- -Répétitivité

- -Cohérence des voies

- -Erreur < 3 %

(Troncature, dynamique utilisée, calcul Flottant Matlab)

-Projet validé par un test sur carte.

### Traitement du signal et communication numérique sur FPGA

Présentation du stage

- Contexte

- Finalité

Analyse spectrale voie courte/voie longue sur PPGA

Liaison Gigabit Ethernet sur FPGA

Conclusion et perpectives

# Traitement du signal et communication numérique sur FPGA

Liaison Gigabit Ethernet sur FPGA

Contexte:

### Traitement du signal et communication numérique sur FPGA

Liaison Gigabit Ethernet sur FPGA Contexte:

- Flexibilité de l'architecure point à point vs bus partagé pour le VME

- Performances débit utile > débit VME

# Traitement du signal et communication numérique sur FPGA

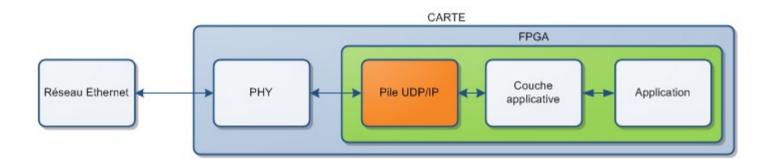

Liaison Gigabit Ethernet sur FPGA Contexte:

Développement d'une pile UDP/IP hardware

# Traitement du signal et communication numérique sur FPGA

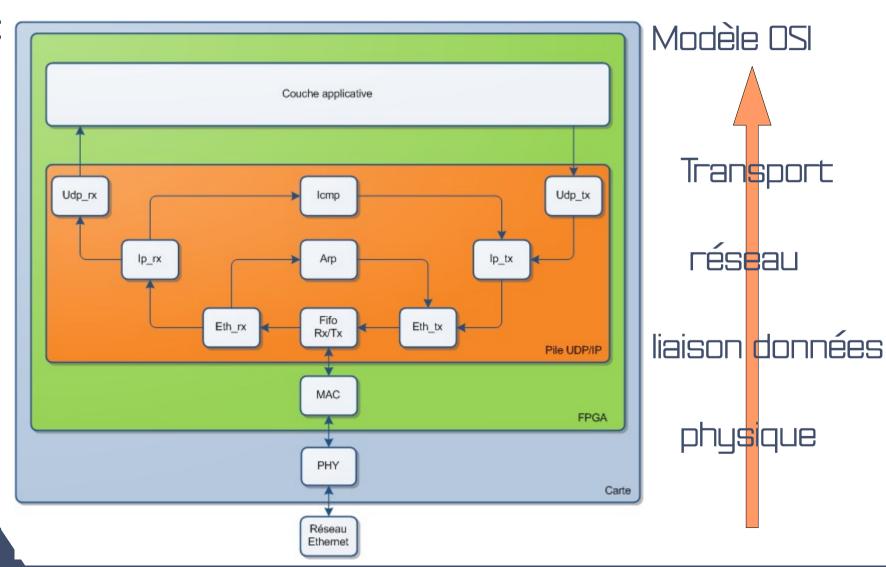

Liaison Gigabit Ethernet sur FPGA Architecture:

... ... correctement acheminées[ports UDP]

... ... d'un point A à un point B [IP TTL,...]

... intègres (MAC, checksum)

Transmettre des données [Médium ]

Modèle OSI

Transport

réseau

liaison données

physique

# Traitement du signal et communication numérique sur FPGA

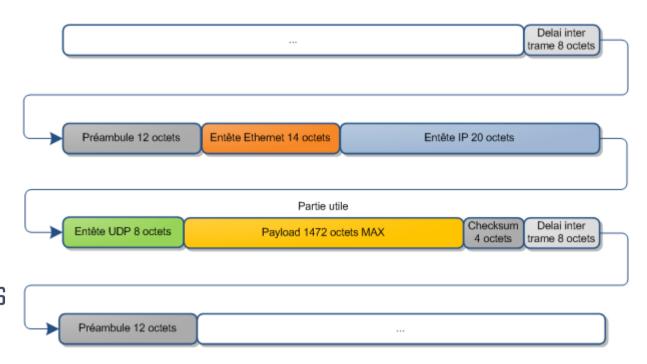

Liaison Gigabit Ethernet sur FPGA Architecture:

Débit utile théorique: 117 Mo / s

Streaming et remplissage des trames

# Traitement du signal et communication numérique sur FPGA

Architecture:

# Traitement du signal et communication numérique sur FPGA

Liaison Gigabit Ethernet sur FPGA Résultats:

- Implémentation sur une carte d'évaluation Spartan 3A DSP

- Liaison Full duplex **II7** mo/s

(Temps de latence masqué par le préambule + checksum

- + delai inter- trame]

- système s'identifiant sur un réseau

- pile évolutive pour prendre en compte d'autres protocoles réseaux

Implémentation sur une affaire interne.

### Traitement du signal et communication numérique sur FPGA

Liaison Gigabit Ethernet sur FPGA Amélioration d'une carte de traitement

2 ports G-Ethernet

Système de routage des données FPGAs <--> Ports G-Ethernet

Configuration VME

- -Paramètres G-Ethernet

- -Tables de routage

### Traitement du signal et communication numérique sur FPGA

Présentation du stage

- Contexte

- Finalité

Analyse spectrale voie courte/voie longue sur PPGA

Liaison Gigabit Ethernet sur FPGA

Conclusion et perpectives

### Traitement du signal et communication numérique sur FPGA

Conclusion et perspectives:

- Montée en puissance des PGAs dans les applications de traitement du signal et de communication numérique.

- Véritables systèmes à part entière.

- Nouveaux outils, nouvelle philosophie de conception.

# Traitement du signal et communication numérique sur FPGA